近日,西安统一大学国家半导体有限公司(以下简称“ Unisex Nationalchip”)在第63届国际电子设备大会(IEDM2020)上发表了技术论文-“采用具有34GB容量的3D混合键合技术” “ / s / 1Gb具有带宽和0.88pJ / b能量效率接口的异构集成嵌入式LPDDR4 / LPDDR4XDRAM”。 (用于LPDDR4 / 4X的使用HybridBonding3D集成的堆叠式嵌入式DRAM阵列,具有34GB / s / 1Gb0.88pJ / b逻辑至内存接口)。

本文的发表是Unigroup Guoxin在超高带宽和超低功耗DRAM方向上的技术积累和不断创新的最新突破。受传统计算机系统的冯·诺依曼体系结构的限制,存储器带宽和计算要求(即“存储墙”问题)之间的差距变得越来越突出。

使用硅通孔(TSV)技术的高带宽存储器(HBM)是业界提供的可选解决方案,但是其每个数据引脚的工作频率仍然很高(大约4Gbps),这具有功耗大的缺点。例如,HBM使用x10um微凸块(Micro-Bump)堆叠DRAM,它具有数量有限的数据IO和较大的寄生电容和功耗,从而限制了带宽的增加。

依靠多年对存储器和ASIC架构的深入研究,西安紫光国信开发了一种异构集成嵌入式DRAM平台(SeDRAM),该平台可提供业界最高的单位带宽和能效,并旨在与以下产品完全兼容国际JEDEC标准。 4GbitLPDDR4芯片。

图1. SeDRAM技术流程示意图Ziguang Guoxin在论文中介绍了SeDRAM平台的实现流程(图1):首先,在不同的流程和配备了外围电路的逻辑晶体下,贴出DRAM存储器晶圆(DRAMWafer)。圆形(LogicWafer),并通过异质集成工艺(例如平面化,曝光和蚀刻),将两个晶片分别制成接触孔(LTVIA和LBVIA)以用于后续步骤;然后,将逻辑晶片翻转并通过Cu-Cu互连方法,将两个晶片直接键合。

最后,将逻辑晶片减薄至约3um的厚度,并从逻辑晶片的背面开口完成PAD的生产。与HBM的MicroBump工艺相比,通过直接键合的异质集成工艺,接触孔可以达到11万/ mm2,密度提高了一百倍,连接电阻低至0.5欧姆。

从逻辑电路到存储阵列,这实现了高达每Gbit 34GB / s的带宽和0.88pJ / bit的能效。图2.使用SeDRAM技术开发的4GbLPDDR4产品的晶圆(左)和布局(右)。

紫光国信开发的4GbitLPDDR4是业界首个异构集成标准接口DRAM产品(图2)。该产品为双通道,数据位宽为X16,并且在每个芯片中集成了超过64,000个异构集成接触孔。

在晶圆测试阶段,该产品表现出出色的性能,读取时间比测试机支持的最快时钟周期超出了0.56ns。在颗粒测试阶段,产品通过了多种测试条件,包括高温(95°C),高压(VDD2 = 1.2v,VDD1 = 2v)和低压(VDD2 = 1.05v,VDD1 = 1.65v)。

#39;最高级别的4266Mbps数据速率测试。该产品在高温测试条件下的保留时间为96ms,这在相同的DRAM工艺下比传统的平面产品更具优势。

图3.4 GbLPDDR4产品的读取时间测试结果(左)和数据保留时间测试结果(右)。感谢武汉新鑫和台湾功率半导体制造有限公司对逻辑芯片和异构集成的支持,并与内存芯片代工厂合作。

IEDM2020成功发布,这是Unisplendour Nationalchip在超高带宽和超低功耗DRAM方向上的技术积累和不断创新的最新突破。通过开发4GbitLPDDR4产品,SeDRAM平台不仅为传统DRAM产品的开发提供了一条新途径,而且还为满足人工智能(AI)和高性能计算(HPC)对高带宽和高能效的要求提供了有效的解决方案。

)。原始标题:西安统一大学国家核心在IEDM2020上发表了异构集成嵌入式DRAM(SeDRAM)论文。

文章来源:[微信公众号:西安统一大学国家核心半导体]欢迎您增加关注!请指出转载文章的来源。

公司: 深圳市捷比信实业有限公司

电话: 0755-29796190

邮箱: ys@jepsun.com

产品经理: 汤经理

QQ: 2057469664

地址: 深圳市宝安区翻身路富源大厦1栋7楼

更多资讯

获取最新公司新闻和行业资料。

- 现货SMC磁性开关D-90、D-A93 D-A73:高效可靠的自动化控制选择 现货供应的SMC磁性开关D-90、D-A93和D-A73型号是工业自动化领域中不可或缺的传感设备。这些开关主要用于检测气缸活塞的位置,通过内置的磁感应元件来实现非接触式的信号传输。它们在设计上具备小巧紧凑的特点,能够轻松安装...

- 嵌入式通信技术:实现设备间高效互联的新范式 嵌入式通信:连接万物的智能神经网络嵌入式通信技术正成为物联网(IoT)、工业自动化和智能终端发展的核心驱动力。通过将通信模块深度集成于主控芯片或传感器内部,实现了低功耗、高可靠性的数据交互。1. 嵌入式通信的...

- 深入解析:数码管电阻计算与影像译码器在嵌入式系统中的集成应用 数码管电阻计算与影像译码器的嵌入式集成实践在嵌入式系统开发中,将影像译码器与数码管显示模块结合,实现高效、直观的人机交互界面,已成为主流趋势。本文从实际工程角度出发,深入探讨两者的集成逻辑与关键设计要...

- 深入解析时钟发生器频率合成器在高速通信系统中的关键作用 时钟发生器频率合成器在高速通信中的核心价值在5G基站、光通信模块和高速数据传输设备中,时钟发生器与频率合成器不仅是时间基准的提供者,更是系统性能的决定性因素。其稳定性和精度直接影响误码率、信号完整性与系统...

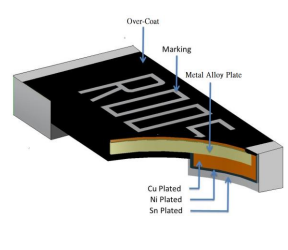

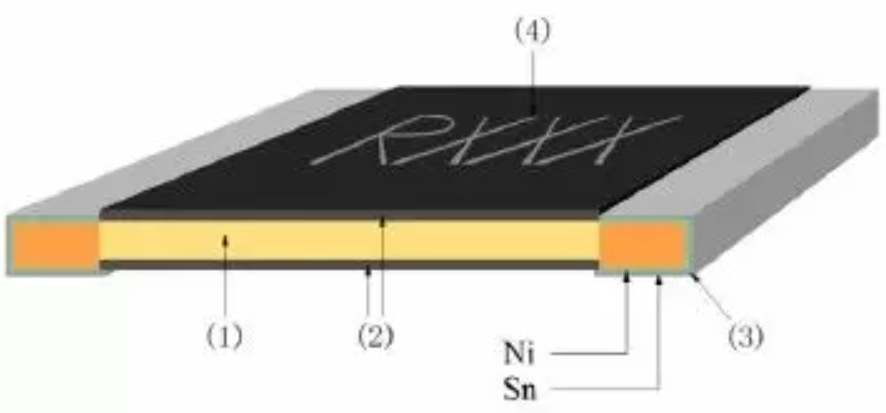

- 深入理解嵌入式晶圆电阻的制造工艺与技术趋势 深入理解嵌入式晶圆电阻的制造工艺与技术趋势随着微电子技术的不断发展,嵌入式晶圆电阻正朝着更高精度、更小尺寸和更强可靠性的方向演进。其制造过程融合了半导体加工的核心技术,是现代IC设计不可或缺的一部分。1. 关...

- BLDC整合式马达驱动器PCB设计关键技术解析 BLDC整合式马达驱动器PCB设计关键技术解析在现代工业自动化与智能家电领域,无刷直流电机(BLDC)因其高效率、低噪音和长寿命等优势被广泛应用。而整合式马达驱动器的设计,尤其是其印刷电路板(PCB)布局,直接决定了系统...

- 深入解析光颉Viking LRP系列合金电阻器的技术参数与选型指南 光颉Viking LRP系列技术参数详解在选择适合特定应用的大功率电阻器时,了解其关键技术指标至关重要。以下是光颉Viking LRP系列的主要参数说明:关键参数一览额定功率:从10W至100W不等,覆盖多种功率需求场景。阻值范围:1Ω~...

- 如何选择适合嵌入式系统的高性能PMIC电源管理芯片 选型指南:构建稳定可靠的嵌入式电源系统在工业控制、智能家居、医疗设备等嵌入式应用场景中,电源稳定性直接影响系统可靠性与寿命。因此,合理选择一款合适的PMIC电源管理芯片至关重要。以下从多个维度提供选型建议。...

- 深入解析车用保险丝与比较器的材料科学:从合金选择到系统集成 背景与重要性在汽车电子系统日益复杂化的今天,保险丝和比较器作为基础但至关重要的组件,承担着过流保护与状态监控的核心功能。它们的材料选择不仅影响单个元件性能,更关乎整车电气系统的稳定性与安全性。本文将从...

- 深入解析RS-232接口与USB 3.2在现代通信中的差异与应用 RS-232接口与USB 3.2的核心区别详解在工业控制、嵌入式系统和传统设备通信中,RS-232接口曾长期扮演关键角色。然而,随着技术的演进,USB 3.2逐渐成为主流数据传输标准。本文将从多个维度对比两者的技术特点、应用场景及优劣。...

- 整合式IF开关矩阵:实现高性能射频系统的关键技术 整合式IF开关矩阵在现代通信系统中的核心作用随着无线通信技术的飞速发展,射频(RF)与中频(IF)信号处理系统的复杂性日益增加。整合式IF开关矩阵作为一种集成化解决方案,正在成为高性能通信设备设计的核心组件。1. 功...

- 深入解析电阻阵列CN..A系列与SWR..A系列、CRW..A系列的核心差异 引言在电子元器件领域,电阻阵列因其高集成度、稳定性和空间节省优势,广泛应用于精密电路、工业控制及通信设备中。其中,CN..A系列、SWR..A系列和CRW..A系列是市场上常见的三种电阻阵列型号。尽管它们均属于电阻阵列类别,...

- 深入解析TFAN系列电阻阵列:高性能与高集成度的完美结合 TFAN系列电阻阵列概述TFAN系列电阻阵列是专为现代电子系统设计的高精度、高可靠性集成电阻组件,广泛应用于消费电子、工业控制、通信设备及汽车电子等领域。该系列采用先进的薄膜技术制造,具有出色的温度稳定性、低噪声...

- 信昌取样电阻在5G通信中的关键应用与技术优势解析 信昌取样电阻在5G通信系统中的核心作用随着5G通信技术的快速普及,对元器件的精度、稳定性及高频性能提出了更高要求。信昌元件作为国内领先的电子元器件供应商,其生产的高精度取样电阻在5G基站、终端设备及射频前端模...

- 分立组件负载开关与集成式方案对比:如何选择更适合的方案? 分立组件负载开关与集成式方案的全面对比随着电子系统复杂度不断提升,负载开关的选择成为电源管理设计中的关键环节。分立组件负载开关虽不如集成方案紧凑,但在特定场景下展现出不可替代的优势。本文将从多个维度进...

- 从零构建高效音讯系统:关键技术与架构设计指南 从零构建高效音讯系统:关键技术与架构设计指南构建一个高性能音讯系统并非简单地集成音频库,而是一项涉及硬件、软件、网络与人机交互的综合性工程。以下是从零开始设计音讯系统的五大关键步骤。1. 明确应用场景与需...

- 深入解析:如何使用UART串口桥接器构建稳定通信链路 构建稳定通信链路的关键步骤在实际项目中,仅拥有一个UART串口桥接器并不足以保证通信的可靠性。合理的设计与调试流程是实现稳定通信的核心。硬件连接与布线规范正确的物理连接是通信成功的前提:使用屏蔽双绞线减少信...

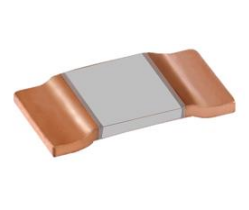

- RLF合金四端式电流感应电阻:实现精准电流采样的关键技术组件 RLF合金四端式电流感应电阻:实现精准电流采样的关键技术组件随着电力电子设备向高效化、集成化方向发展,对电流感应器件的性能要求日益严苛。RLF(Resistance Low-Fidelity Alloy)合金四端式电流感应电阻凭借其卓越的电气特性与...

- 如何根据应用场景选择合适的耐脉冲电阻?PWR..A、SWR..A与CRW..A系列选型指南 基于应用场景的耐脉冲电阻选型策略面对PWR..A、SWR..A和CRW..A三大系列,正确选择不仅影响设备性能,还直接关系到系统安全与维护成本。以下从实际应用出发,提供科学选型建议。1. 高压/高能环境:优先选用PWR..A系列当设备部署...

- 时钟发生器与频率合成技术详解:原理、应用及未来趋势 时钟发生器与频率合成技术概述在现代电子系统中,时钟发生器(Clock Generator)和频率合成器(Frequency Synthesizer)是确保系统同步运行的核心组件。它们不仅为数字电路提供精确的时间基准,还在通信、雷达、测试测量和高性能...