选择满足FPGA应用需求的电源时,我们必须考虑许多因素。成本,尺寸和效率始终是电源设计过程中需要注意的因素。

但是,在FPGA应用中,某些电源轨会有不同的要求。核心电源轨通常需要在线路,负载和温度范围内保持更严格的精度。

某些电源轨(例如收发器)对噪声更敏感,因此需要将其输出保持在一定的噪声阈值以下。还应注意,某些具有共模电压的电源轨可以组合,并可以用铁氧体磁珠隔离,以进行滤波或用作负载开关。

当设计满足公差要求时,必须考虑所有固定和动态工作条件。首先,选择基准精度小于1%的稳压器,该稳压器为客户提供了最大的设计余量,使其可以应对诸如负载瞬变之类的动态工作条件。

设计高速收发器电源轨时需要小心,因为这些敏感电源轨上的噪声会降低性能并增加抖动。低压降稳压器(LDO)是这些电源轨的理想选择。

但是,当需要更高的电流时,只要在10kHz至80MHz的频率范围内将输出纹波的典型值保持在10mVpk-pk以下,就可以使用开关电源。专用的FPGA数据手册将包含与收发器要求有关的详细技术规范。

电源排序是FPGA电源设计的另一个重要方面。由于有多个电源轨可为FPGA供电,因此以下建议的电源序列会在启动时消耗最小电流,从而防止损坏器件。

图2显示了Virtex 7系列FPGA上逻辑电路和收发器电源轨的推荐上电顺序。 Zynq 7000系列SoC的处理器序列如图2所示。

图1:建议的Virtex 7 FPGA上电序列。 * VCCINT和VMGTAVCC可以同时通电,只要它们在VMGTAVTT之前启动,它们的通电顺序就可以互换。

图2:Zynq 7000系列SoC的推荐上电顺序。对于Xilinx 7 / Zynq 7000系列器件,这些电源轨必须单调上升,并且必须在0.2ms至50ms的周期范围内加电,而对于Xilinx Ultrascale FPGA系列器件,此周期范围是0.2ms至40ms。

建议关闭电源顺序和打开电源顺序的顺序。

公司: 深圳市捷比信实业有限公司

电话: 0755-29796190

邮箱: ys@jepsun.com

产品经理: 汤经理

QQ: 2057469664

地址: 深圳市宝安区翻身路富源大厦1栋7楼

更多资讯

获取最新公司新闻和行业资料。

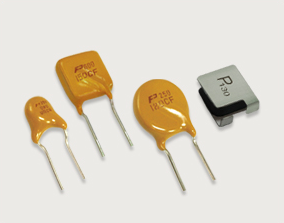

- 自恢复保险丝的使用过程中需要注意哪些事项? 在使用自恢复保险丝的过程中需要注意以下几点:选择合适的额定电压和电流:应根据被保护电路的额定电压和电流选择合适的自恢复保险丝,以确保保险丝能够在过流或短路故障时正常工作。避免误用:应避免将自恢复保险丝...

- 如何正确选型无源晶振?关键参数与设计注意事项全解析 无源晶振选型前的五大关键因素尽管无源晶振结构简单,但在实际应用中若选型不当,可能导致系统无法启动、时钟漂移甚至设备死机。因此,科学选型至关重要。1. 频率精度(Frequency Tolerance)表示晶振标称频率与实际输出频率...

- 电阻有没有2W功率的?应用场景及注意事项 电阻确实有2W功率的规格。在电子元件中,电阻的功率是一个非常重要的参数,它表示电阻能够承受的最大功率值。通常情况下,电阻的功率规格包括1/8W、1/4W、1/2W、1W、2W、5W、10W等。2W功率的电阻意味着该电阻能够在不损坏的情...

- 贴片磁珠选择要注意哪些 贴片磁珠的功能主要是消除传输线结构(PCB电路)中存在的RF噪声。RF能量是叠加在DC传输电平上的AC正弦波分量。直流分量是所需的有用信号,而射频能量是沿线路传输和辐射的无用电磁干扰(EMI)。为了消除这些不必要的信号能...

- 常见的直流稳压电源电容有哪些 所谓的电容是包含并释放电荷的电子组件,电容的基本功能原理是充电和放电,当然还具有整流和振荡等功能。另外,电容的结构非常简单,并且主要由两个正电极,负电极和布置在它们之间的绝缘介质组成,因此电容的类型主...

- 高频电感使用注意事项 注意环境的湿度和干燥度、高低温、高频或低频环境,以及电感是否应显示电感或阻抗特性。电感器设计承受的最大电流和相应的发热情况。在使用部分,找出相应的L值和相应材料的使用范围。注意导线(漆包线、纱包线或裸线...

- 贴装35W无感电阻步骤与注意事项 在电子制造过程中,正确地贴装35W无感电阻是非常重要的一步。无感电阻因其低电感特性,在高频电路中有着广泛的应用。下面是关于如何正确贴装35W无感电阻的一些指导和建议。首先,确保工作台面干净整洁,所有需要的工具...

- 铝壳电阻生产工艺及选用注意事项 什么是铝壳电阻器?铝壳电阻器的生产工艺是什么?使用铝制外壳电阻器时应注意什么? 1、什么是铝壳电阻器?铝壳电阻器,由铝合金制成(金铝壳),表面有散热槽,体积小,功率大,耐高温,过载能力强,耐...

- 批发DZ47-63空气开关的选择与注意事项 当谈及电气设备的采购时,批发DZ47-63型空气开关是一个常见的需求。这类空气开关广泛应用于工业、商业以及住宅等不同场景中的电路保护系统。对于那些需要大量购买此类产品的用户而言,比如建筑承包商、电气工程公司或是...

- 批发HY2-15倒顺开关的选择与注意事项 在探讨关于*批发HY2-15倒顺开关的相关信息时,我们首先需要了解这款产品的基本功能和适用范围。HY2-15倒顺开关主要用于小型电动机的正反转控制,广泛应用于各种机械设备中,如输送带、搅拌机等。对于这类开关的选择,不仅...

- 电解电容的使用及注意事项 一、电解电容器的使用极性电解电容器通常用于功率电路或中低频电路中,用于滤波、去耦、信号耦合、调整时间常数和阻断直流电。通常不能用于交流电路。当用作直流电路中的滤波电容器时,阳极(正极)应连接到电源电压...

- TR20 TO-220 20W功率电阻选型指南与使用注意事项 TR20 TO-220 20W功率电阻全面选型建议在选择光颉TR20系列20W功率电阻时,需综合考虑功率需求、环境温度、安装方式及电气精度等关键因素。以下为专业选型指导:1. 功率与散热匹配虽然额定功率为20W,但实际应用中应留有20%-30%余量...

- TVS管有哪些类型? TVS管是一种通用的电路保护器件,可以根据不同的应用需求和电路特性来分为不同的类型。常见的TVS管类型包括:齐纳二极管型TVS管:这种TVS管是由一个二极管和一个小型电容组成的,可以用于高频电路中的浪涌保护。瞬态电压...

- TVS管有哪些应用? TVS管广泛应用于电子电路中,主要用于稳压、调节电流、过压保护、瞬态过电压保护等功能。例如,TVS管可以用于电池供电系统、照明设备、开关电源、高压电路等电路中,起到稳压、降压、过压保护等作用。在这些电路中,TVS...

- KAMAYA釜屋HFC32贴片保险丝选型指南与使用注意事项 KAMAYA釜屋HFC32贴片保险丝选型关键参数在选择HFC32系列贴片保险丝时,需综合考虑多个技术指标以确保电路安全与系统稳定性。1. 额定电流与熔断特性匹配根据实际工作电流选择合适等级(如1.0A、1.5A、2.0A、3.15A),建议预留15%-20...

- 如何正确选型35W无感电阻?关键参数与注意事项 如何正确选型35W无感电阻?关键参数与注意事项面对市场上种类繁多的35W无感电阻产品,合理选型是保障系统安全与效率的关键。本文将从技术参数、环境条件和实际应用出发,帮助工程师科学选择合适的型号。1. 核心选型参数...

- 220伏电机电容正确接线方法及注意事项 标题:在工业生产和日常生活中,220伏电机的应用十分广泛。其中,电容作为电机的重要辅助元件,其正确接线对于电机的稳定运行至关重要。本文将详细介绍220伏电机电容的接线步骤、接线原则以及相关注意事项。首先,明确...

- TOLLMOS管的分类有哪些? TOLL-MOS管(Trench-Oxide Low-Leakage MOS)是一种特殊的MOS管,它的结构是在半导体衬底上蚀刻出许多深度为几微米的沟道,然后在沟道中填充一层薄的绝缘氧化层。TOLL-MOS管的分类主要是根据其结构和性能的不同,可以分为以下几种:N...

- 保险丝有哪些认证? 保险丝的认证主要有以下几种:CCC认证:中国强制性产品认证,是国家对电器产品安全性能的认可,适用于所有电器产品,包括保险丝。UL认证:美国UL认证,是国际公认的安全认证标志,适用于出口到北美地区的保险丝产品。VD...

- 保险丝有哪些类型? 保险丝有多种类型,以下是其中一些常见的类型:普通保险丝:这是最常见的保险丝类型,其特点是价格便宜,熔断速度慢。普通保险丝通常使用铅锑合金制成,熔点较低,一般为60°C至80°C。快速保险丝:这种保险丝的熔断速度...